Abstract

An islanding detection method in ungrounded power distribution system based on single-phase operating mechanisms of the circuit breaker (CB) is proposed in this paper. When CB opens three phase circuits to form an island, one phase circuit is opened firstly and the other two phase circuits are opened secondly after certain duration. During the period when only one phase circuit is opened, negative sequence voltage with certain duration is obtained at DG side because of the asymmetric operation of the system. After all three phase circuits are opened, the voltage variation direction of the two phases that are secondly disconnected from the grid follows the voltage variation direction of the firstly disconnected phase. Based on the above voltage characteristics, an islanding detection scheme is proposed to identify genuine islanding from system disturbances. The performance of the proposed scheme is tested in PSCAD/EMTDC using a 10 kV distribution network with synchronous DG interconnection. Simulation results demonstrate the proposed method is effective and reliable to detect islanding formation.

Similar content being viewed by others

1 Introduction

According to the development strategy of renewable energy industry in China, distributed generation (DG) projects are about to develop more quickly in the following years [1]. As DG plays an increasingly important role in power distribution network, islanding detection capability becomes an essential requirement for distributed generator. Islanding refers to the condition when a portion of power system is energized solely by one or more DGs, while that portion of the grid is electrically separated from the rest of the power system due to faults, utility control measures, as well as system maintenance and repair operations [2, 3]. For fault-induced islanding, protection relays equipped by DG, such as overcurrent relay, are responsible to isolate the DG from the fault [4, 5]. And anti-islanding protection is equipped to disconnect DG immediately after islanding formation, especially for islanding that is not induced by the fault, which is also used to evaluate the performance of the anti-islanding protection relay [6, 7].

In order to tackle this problem, islanding detection techniques have been extensively studied in recent years, which can be classified as local methods and remote methods [6]. Local methods consist of active methods and passive methods. Active methods inject small disturbances into the grid at DG site, and then determine islanding formation based on locally measured responses [8–10]. Active methods are widely used for inverter-based DGs, but few of them have been fully developed for synchronous DGs. Passive strategies detect islanding based on locally measured parameters [11–13]. These methods are usually of low-cost. However, they are incapable of differentiating islanding formation from disturbances. As a result, islanding detection performance can be severely deteriorated under system disturbance scenarios. This defect has been proved in field application [5].

Remote methods use communication means to transmit specific signals from the substation to DG, and a receiver located at DG site to determine whether an island forms or not in accordance with the received signal. One remote technique is transfer trip scheme, which uses telecommunication means to trip the islanded DG [13]. This scheme monitors the status of all openable devices between the DG and the utility using a central algorithm, if a switching operation causes disconnection to the substation, and the central algorithm will determine the islanded areas and then send tripping signal to the islanded DG. Although it is simple in concept, this scheme can be expensive. Besides, when telecommunication coverage is weak, the specific signal will not be reliably received, and the islanding detection performance will be jeopardized [11].

Another promising remote technique is power line signaling based scheme [14, 15]. This scheme continuously transmits specific signal from upstream substation to downstream DG by a dedicated signal generator. Power line is used as the communication link. Once the upstream circuit breaker (CB) opens to form an island, the DG is unable to receive the signal. As a result, a trip command is sent to disconnect the DG. This scheme outperforms other methods because the injected signal can distinguish genuine islanding and disturbance. However, it is not an economical solution, especially when the amount of interconnected DG is small. Besides, when system fault disturbance occurs, the transmitted signal over the power line may be distorted and interrupted, which will lead to mal-operation.

Following the idea of signal injection, this paper proposes an islanding detection strategy based on single-phase operating mechanisms of CB. With the development of micro-processor based control technology and the increased requirement of customers on power supply reliability, it is feasible for medium-voltage CB to employ single-phase operating mechanisms and to open three phase circuits asymmetrically [11, 16]. Following islanding formation induced by the asymmetric tripping of CB, specific signal is obtained at DG side to identify genuine islanding from system disturbances.

The rest of the paper is developed as follows. Section 2 explains the basic principle of the proposed method, and Section 3 presents the islanding detection algorithm. Then, the islanding detection scheme is presented in Section 4, and A 10 kV ungrounded power distribution network with synchronous DG interconnection is employed to test the proposed method in Section 5. Tested scenarios include islanding formation, load variation and fault disturbance cases. Finally, conclusion is made in Section 6.

2 Basic principle

Before islanding, both the main grid and DG feed the load together. When islanding forms, the proposed asymmetric tripping mode of CB at the grid side operates as follows. One phase circuit such as phase A is opened in advance, then, the other two phase circuits are opened after a fixed delay, for example 60 ms (3 cycles under 50 Hz system). Finally, islanding is formed when all three phase circuits are opened.

Accordingly, three phase voltages at DG side will experience the following changes in response to islanding formation. Before islanding, when distribution system normally operates, the three phase voltages are balanced and within the permissible operation zone of voltage, hence the negative sequence voltage V 2 is negligible. During islanding, when only phase A circuit is opened while phase B and phase C circuits are still connected to the grid, phase A voltage at DG side will change either with an increasing or decreasing direction compared to the rated phase voltage, for reactive power distribution in power system will change, even if active power is balanced between DG and the load. And V 2 will be induced and last at least until the time, at which phase B and phase C circuits are opened, due to the asymmetrical operation.

After all three phase circuits are opened and islanding is finally formed, phase B and phase C voltages will follow the same varying direction of phase A voltage because three phase voltages at DG side become balanced again. Besides, negative sequence voltage V 2 will disappear after three phase voltages at DG side are balanced.

To conclude, based on CB’s asymmetric tripping, the islanding formation will result in two evident voltage characteristics at DG side. One is that negative sequence voltage V 2 will appear at first with certain duration. The other one is that three phase voltages will have the same variation direction but with a fixed time gap.

Besides islanding formation, the above voltage characteristics of DG side are further evaluated under other operation scenarios, such as normal load variation and fault disturbance [11, 17]. Although normal load variation scenarios include balanced and unbalanced load variation, on the one hand balanced load variation will not generate negative sequence voltage V 2, on the other hand unbalanced load variation will have different phase voltages variation characteristics compared with islanding formation. As for fault disturbance, it can be divided into two stages, with the first stage representing fault existence and the second representing fault isolation. During fault existence, depending on the specific fault type, the faulted phase voltage will decrease from the rated voltage, while the sound phase voltages may maintain or even increase from the rated voltage in neutral ungrounded system. After fault isolation, three phase voltages will recover to the same magnitude. Accordingly, three phase voltage variation directions are always not the same.

Therefore, the basic principle of the proposed islanding detection method employs unique voltage characteristics at DG side during islanding formation.

3 Islanding detection algorithm

The foregoing two voltage characteristics of islanding formation are implemented by defining the first and second criterion respectively. In the first criterion, voltage unbalance (V U ) is calculated in (1) to implement the characteristic of negative sequence voltage:

where V 2 and V 1 are root mean square (RMS) values of negative and positive sequence voltage at DG side, respectively.

Assume SET1 is the threshold for V U , the first criterion is established as:

where subscript t indicates the duration of V U in response to the asymmetric tripping process of CB, and T 1 denotes the duration threshold. In the paper, the asymmetric tripping duration of CB is 60 ms, and T 1 is set as 50 ms by considering the transient process of voltage variation.

The second criterion on three phase voltages variation characteristics is implemented by defining phase voltage variation direction (PVVD). Let [V min, V max] denotes the normal phase voltage operation zone, where V min and V max represent the lowest and highest RMS values of phase voltage respectively. When phase voltage is within the voltage operation zone, the corresponding PVVD result is “0”; Otherwise, the PVVD would be “−1” if phase voltage below V min and “1” if above V max. For illustration purposes, A PVVD, B PVVD and C PVVD are used to denote PVVD results of phase A, B and C voltages respectively. S PVVD represents the integrated results of A PVVD, B PVVD and C PVVD, for instance S PVVD (−1, 1, 0) denotes that A PVVD, B PVVD, and C PVVD are −1, 1 and 0 respectively. Based on this definition, the second criterion is established in (3) and (4), indicating two possible variation directions of phase A voltage after phase A’s CB is opened, respectively. Specifically, (3) indicates the increment of phase A voltage, while (4) indicates the decrement of phase A voltage from the rated voltage.

In (3), subscript dt represents the set time delay to calculate the first S PVVD after V U exceeds SET1 to avoid the effect of transient process; T denotes the preset asymmetric tripping delay between the operation of phase A and phase B, C circuit breakers, thus, subscript dt+T represents the time to calculate the second S PVVD after V U exceeds SET1. Accordingly, (3) means that during islanding formation, phase A voltage at time dt increases above the voltage setting zone, and three phase voltages at time dt+T increase above the setting zone after phase-A’s CB is opened. In the paper, T is set as 60 ms and dt 30 ms for 50 Hz power system. In (4), notations dt and T are the same as that in (3). But to discriminate islanding formation from fault disturbance in power distribution system with neutral ungrounded, at time dt both phase B and phase C voltages are introduced and investigated. For islanding formation, at time dt both phase B and C circuits are remained connected to the main grid, so B PVVD,dt and C PVVD,dt will maintain the system voltage, unequal to “−1”. However, given three-phase fault occurs, B PVVD,dt and C PVVD,dt will be “−1”.

The above thresholds can be set according to the National Standard of Power Quality [18, 19], which stipulates the admissible phase voltage unbalance and deviation in medium-voltage distribution system. For 10 kV system, the admissible three-phase voltage unbalance should be below 2% under normal load variation. So, SET1 is set as 2% in the paper. For the permissible operation zone of phase voltage [V min, V max], it is worth noting that the permissible phase voltage is between 88% and 110% of rated RMS value according to IEEE std 1547-2003 [2], whereas in China both positive and negative power supply voltage deviation should be less than 7% of the rated value [19]. And in the paper, V min and V max are set as 93% and 107% of rated RMS value of phase voltage respectively according to [19].

4 Islanding detection scheme

By combining the two criteria in a logical order, the islanding detection scheme is proposed in Fig. 1. Firstly, V U is derived in real time from sampled three phase voltages and continuously compared with the threshold SET1. If V U is less than SET1, it is determined that the system is under normal condition and the scheme moves to analyze the next sampling point. Once V U exceeds SET1, a timer starts counting up to set values by using a loop variable n. And in the scheme, three critical time should be calculated. The first critical time is dt. During the time dt, V U should exceed SET1 continuously. If V U cannot keep exceeding SET1 before n reaches to dt, it is determined as system disturbance and the scheme will be reset immediately. If V U meets the requirement, at time dt, S PVVD will be calculated as S PVVD,1, which consists of A PVVD,1, B PVVD,1 and C PVVD,1. For S PVVD,1, if A PVVD,1 equals to “−1” while both B PVVD,1 and C PVVD,1 do not, or, if A PVVD,1 equals to “1”, S PVVD,1 will be saved for further evaluation. All other obtained PVVD results will be concluded as disturbance and the scheme reset immediately.

After S PVVD,1 is saved, the second critical time T 1 is judged, which is the duration threshold for V U exceeding SET1. During the process n increasing to T 1, if any V U decreases below SET1, the scheme resets immediately. Otherwise, the first criterion will be qualified when V U keeps exceeding SET1 until T 1 is reached.

After the qualification of the first criterion, the scheme goes on to evaluate the second criterion at the third critical time point dt plus T. At this time point, the second S PVVD is calculated as S PVVD,2. Next, both S PVVD,1 and S PVVD,2 are used to evaluate the second criterion. If A PVVD,1 equals to “−1” and S PVVD,2 equals to (−1, −1, −1), while B PVVD,1 and C PVVD,1 are unequal to “−1”; or, if A PVVD,1 equals to “1” and S PVVD,2 equals to (1, 1, 1), the second criterion will be finally qualified.

If all the foregoing requirements are met, the scheme determines that islanding is formed and a trip signal is issued immediately to disconnect DG.

5 Simulation tests

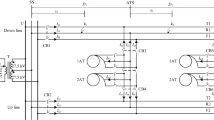

This section assesses the detection performance of the proposed scheme. The investigated system is a modified network from [5]. Fig. 2 shows the single line diagram of the network. A 110 kV, 50 Hz sub-transmission system feeds the 10 kV distribution system through 110/10 kV, Yg/△ transformer. A 1 MVA synchronous DG is connected at node 327. An induction motor is connected at node 337. The CB between node 302 and 327 is equipped with asymmetric tripping mode.

The simulation tests are conducted using PSCAD/EMTDC. Specific simulation models and typical parameters are as follows. Distribution feeders are simulated using Bergeron model. Transformers are modeled using T circuit. Load is simulated using constant impedance load model. The synchronous DG is equipped with an exciter controlled by voltage. Inertia constant of DG is set as 2 s. The induction motor is simulated using a wound rotor machine, and is rated 0.2 MVA. For the CB between node 302 and 327, the asymmetric tripping duration T is 60 ms. In the islanding detection scheme, T 1 and dt are set as 50 and 30 ms, respectively.

The tested scenarios include islanding formation scenario, load variation scenario and fault disturbance scenario. Load variation scenarios include both balanced and unbalanced load variation, as well as motor start. And fault disturbance scenarios include both symmetric and asymmetric fault disturbance cases.

5.1 Islanding formation scenario

In the simulation, the CB between node 302 and 327 is opened asymmetrically at 5 s. Fig. 3 presents a typical simulation result of the proposed method. Islanding starts to form at 5 s and phase voltages at DG side vary in response to the opening of CB. V U begins to vary and exceed SET1 at 5.008 s. After 30 ms, S PVVD (−1, 0, 0) is obtained at 5.038 s, which is saved as S PVVD,1 for further evaluation. Then, the scheme checks the duration of the first criteria. As seen, from 5.008 s to 5.058 s, V U keeps exceeding SET1, so the first criterion is met. Further, S PVVD (−1, −1, −1) is obtained and maintained since 5.092 s, so the second criterion is met at 5.098 s, which is 90 ms delay from the instant V U exceeds SET1. As a result, a trip signal is issued to disconnect DG.

5.2 Normal load variation scenario

Two scenarios of normal load variation scenarios are conducted. One scenario is simulated by adding three-phase or single-phase load to node 1117, which represents balanced and unbalanced load variation respectively. For unbalanced variation, the single-phase load is connected to phase-A circuit. The other scenario is conducted by starting the motor connected at node 337.

In the first scenario, both the local load before load variation and the added load are varied to examine the proposed method. A typical case is simulated by setting the local load as 220% of DG nominal power, and the added three-phase or single-phase load as 90% of DG nominal power. For balanced load variation, in regardless of phase voltage, V U is very insensitive to such scenarios; for unbalanced load variation, V U increases to 0.26%, which is below SET1, so the proposed scheme does not mal-operate in these two cases. Additionally, it is also found in other simulations that as the local load and added load get heavier, the voltage variation becomes greater. But mal-operation of the scheme is prevented in all simulated cases since V U does not exceed the threshold. This is reasonable due to the existence of the main grid. In comparison with the large balanced network, normal local load variation presents very limited impact on the overall voltage unbalance value.

In the second scenario, the induction motor is started from zero speed with the simulation results presented in Fig. 4. The motor is started at 5 s, and all three phase voltages at DG side vary in response to the motor startup. From 5 s to 5.05 s, V U increases but is below SET1. Afterwards, three phase voltages become balanced again and V U becomes 0. As a result, the proposed method does not mal-operate during motor startup.

5.3 Fault disturbance scenario

The fault disturbance scenario is conducted by simulating fault occurring on the location shown in Fig. 2. Simulated fault types include single-phase-to-ground fault, two-phase-short-circuit fault, two-phase-to-ground fault, and three-phase fault. To test the proposed method comprehensively, the duration of fault disturbance is varied from 60 ms to 300 ms, considering the typical fault clearing time in medium-voltage distribution system [5].

Figure 5 shows simulation results of the proposed strategy when single-phase-to-ground fault disturbance occurs, the faulted phase is phase A. As seen, fault occurs from 5 s and exists about 200 ms. During fault, V A quickly decreases to 65% of rated value, while V B and V C increases to 123% and 119%, respectively. After 5.22 s, three phase voltages recover to normal value because the fault is cleared. During and after fault, V U does not exceed SET1, so the proposed method is not activated. As a result, the method prevents nuisance trip under this fault disturbance case.

Figure 6 shows simulation result under two-phase-to-ground fault disturbance with faulted phases of phase A and phase B. The fault is assumed to exist for about 60 ms, which equals to the asymmetric tripping operation duration of CB under islanding formation scenario. After fault occurrence, V A, V B, and V C quickly changes to 80%, 84% and 145% of rated value, respectively. Due to the unbalance of three phase voltages, V U exceeds SET1 at 5.011 s. After 11 ms, V A decreases below V min. Then at 5.031 s, V B also decreases below V min while V C increases above V max, which leads to S PVVD (−1, −1, 1). The same S PVVD is obtained at 5.041 s, which violates the second criterion since the obtained B PVVD is equal to −1. Consequently, the scheme resets at 5.041 s. From this instant on, V U keeps exceeding SET1. Then, at 5.071 s, S PVVD (−1, −1, 1) is obtained which disqualifies the second criterion, so the scheme resets again. From 5.071 s to 5.079 s, V U maintains to exceed SET1 with a duration of only 8 ms, which violates the first criterion. Afterwards, V U keeps less than SET1. Consequently, mal-operation is prevented under this fault scenario.

Besides the foregoing fault disturbance cases, two-phase-short-circuit and three-phase fault disturbance scenarios are also simulated with different fault duration setting. Simulation results demonstrate that the proposed scheme can effectively prevent mal-operation under fault disturbance conditions.

6 Conclusion

This paper proposes an islanding detection strategy based on asymmetric tripping of feeder CB in ungrounded power distribution system. Simulation tests demonstrate that the proposed scheme can detect genuine islanding formation. Additionally, the method will not mal-operate under scenarios of normal load variation, induction motor start and system fault disturbances, which improves the reliability of anti-islanding protection. The viability of the method on other types of DGs such as inverter-based DG will be investigated in the next.

References

China National Renewable Energy Center (2014) China renewable energy industry development report 2014, Beijing

IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems (2003) IEEE Standard 1547–2003

Evaluation of islanding detection methods for photovoltaic utility-interactive power systems. Report IEA PVPS T5-09, International Energy Agency, 2002

State Grid Corporation of China (2011) Operation and control specification for distributed resources connected to distribution network. Beijing

Dysko A, Booth C, Anaya-Lara O et al (2007) Reducing unnecessary disconnection of renewable generation from the power system. IET Renew Power Gener 1(1):41–48

Menon V, Nehrir MH (2007) A hybrid islanding detection technique using voltage unbalance and frequency set point. IEEE Trans Power Syst 22(1):442–448

Jang S, Kim K (2004) An islanding detection method for distributed generations using voltage unbalance and total harmonic distortion of current. IEEE Trans Power Del 19(2):745–752

Chowdhury SP, Chowdhury S, Crossley PA (2009) Islanding protection of active distribution networks with renewable distributed generators: a comprehensive survey. Electr Power Syst Res 79(6):984–992

Pankaj G, Bhatia RS, Jain DK (2015) Average absolute frequency deviation value based active islanding detection technique. IEEE Trans Smart Grid 6(1):26–35

Hyoung S, Park J-W (2013) Improvement on stability and islanding detection performances by advanced inverter control of DG. IEEE Trans Power Syst 28(4):3954–3963

Xu W, Mauch K, Martel S (2004) An assessment of DG islanding detection methods and issues for Canada. Final Report, CANMET Energy Technology Centre-Varennes 2004-074(TR), Natural Resources Canada

Mollah RA, Kashem MM, Abdesselam B (2014) An approach for assessing the effectiveness of multiple-feature-based SVM method for islanding detection of distributed generation. IEEE Trans Ind Appl 50(4):2844–2852

Mozina CJ (2001) Interconnection protection of IPP generators at commercial/industrial facilities. IEEE Trans Ind Appl 37(3):681–689

Xu W, Zhang G, Li C et al (2007) A power line signaling based technique for anti-islanding protection of distributed generators-part I: scheme and analysis. IEEE Trans Power Deliv 22(3):1758–1766

Wang W, Kliber J, Zhang G et al (2007) A power line signaling based technique for anti-islanding protection of distributed generators-part II: field test results. IEEE Trans Power Deliv 22(3):1767–1772

Cheney RM, Thorne JT, Hataway G (2008) Distribution single-phase tripping and reclosing: overcoming obstacles with programmable recloser controls. http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5262328

Li C, Savulak J, Reinmuller R (2014) Unintentional islanding of distributed generation—operating experiences from naturally occurred events. IEEE Trans Power Deliv 29(1):269–274

PRC National Standard (2008) Quality of electric energy supply: admissible three-phase voltage unbalance factor. GB/T 15543-2008

PRC National Standard (2005) Quality of electric energy supply—admissible deviation of supply voltage. GB 12325-90

Author information

Authors and Affiliations

Corresponding author

Additional information

CrossCheck date: 25 August 2015

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

SHANG, Y., SHI, S. & DONG, X. Islanding detection based on asymmetric tripping of feeder circuit breaker in ungrounded power distribution system. J. Mod. Power Syst. Clean Energy 3, 526–532 (2015). https://doi.org/10.1007/s40565-015-0162-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40565-015-0162-7